纳秒级时间间隔测量方案

发布时间:2022-09-02 浏览:10023众所周知,电信号通过任何电路都会造成时间上的延迟,只是延迟大小的区别。在芯片特性的考核中,信号传输延迟有时是大家最为关注的一点。比如比较器、驱动器、电平转换器件等,往往我们需要这些器件的传输延迟越小越好,我们的IC设计师门也在努力地苛刻地“抠”减着延迟时间。比如坤元微的单通道电平转换器TS8111,大部分工作条件下的延迟时间10ns以内,同时数纳秒的延迟时间对自动化测量系统发起新的挑战。

当两个脉冲的上升沿或下降沿的时间差越小,测量该时间差所需要的时钟频率就越高,对测试系统的性能要求也越高。比如测量1ns的时间差时,时钟频率至少需要提高到1GHz,一般的测试系统无法胜任。

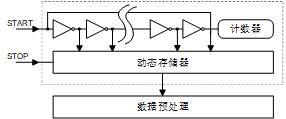

既然电信号通过任何电路都会造成时间上的延迟,聪明的IC设计师们根据这一点反其道而行之,利用该固有延迟测量未知的延迟。Acam公司的高精度时间测量芯片TDC-GPx系列利用信号通过逻辑门电路的绝对传输时间提出了一种新的时间间隔测量方法,测量方法如图1所示。START和STOP是两个待测信号,它们之间的时间间隔由非门的个数决定,而每个非门的传输时间是固定的,由集成电路工艺精确地确定。

图1 TDC-GPx测量原理

以TDC-GP22为例,该TDC芯片有两种测量范围,其中测量范围1:

测量范围:3.5ns to 2.4us

2个stop通道+1个start通道,典型分辨率为90ps

1个stop通道+1个start通道,典型分辨率为45ps

可选择每个通道的上升沿/下降沿触发

可以测量任意两个脉冲之间的时间间隔

测量范围2:

测量范围:700ns to 4ms@4MHz

1个stop通道+1个start通道,典型分辨率为22ps/45ps/90ps

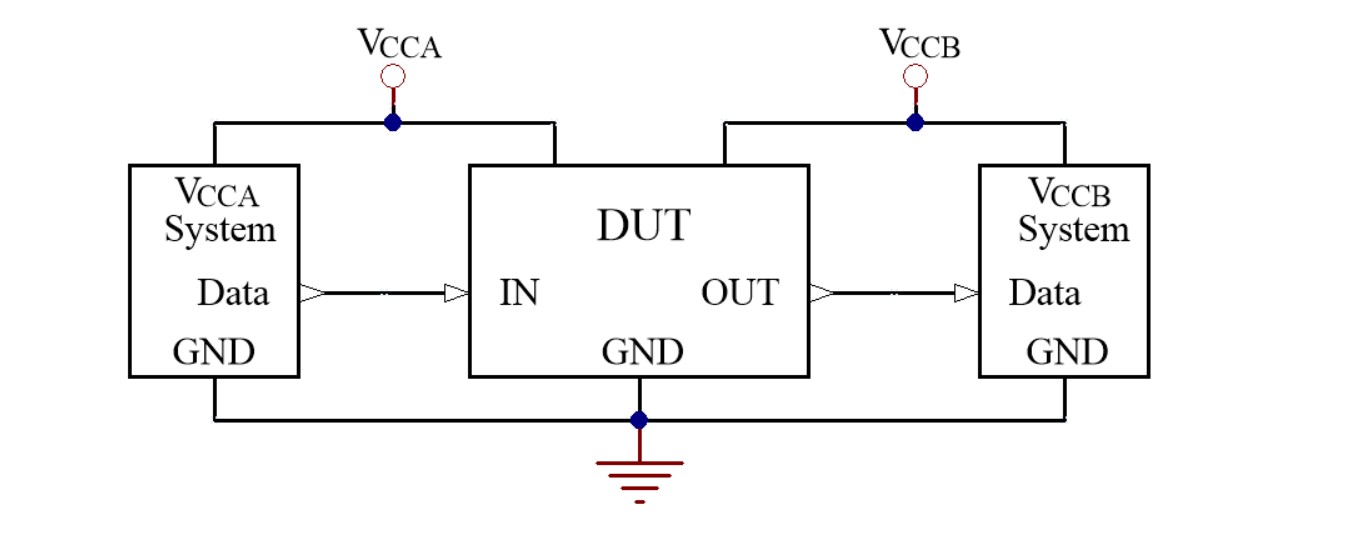

现采用测量范围1中的2个stop通道结合1个start通道的测量方式,实现电平转换器TS8111的传输延迟的测量。TS8111作为两个系统之间电平转换的桥梁,典型应用如图2所示。通常我们仅需要实现两个系统之间电平的转换,不希望有延迟的存在,所以电平转换器件的传输延迟越小越好。

图2 TS8111典型应用

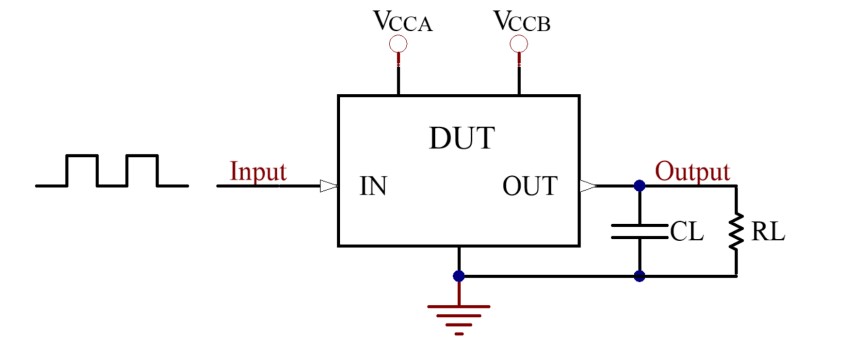

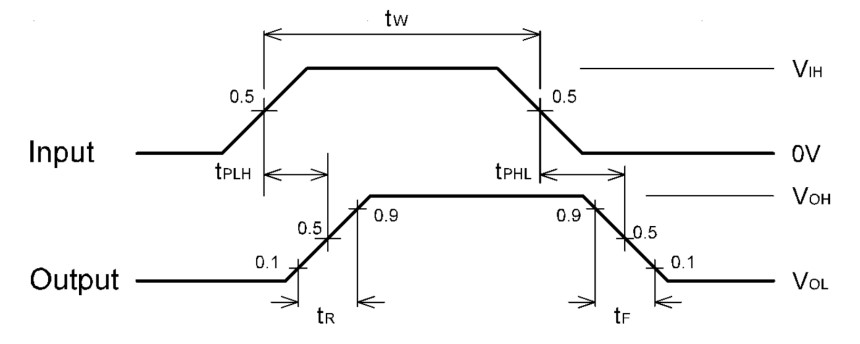

TS8111的传输延迟的测量电路如图3所示,传输延迟的定义如图4中tPLH和tPHL所示。因为传输延迟过小,图3只能用于高带宽的示波器测量方案中。

图3 TS8111传输延迟测量电路

图4 Propagation Delay Time

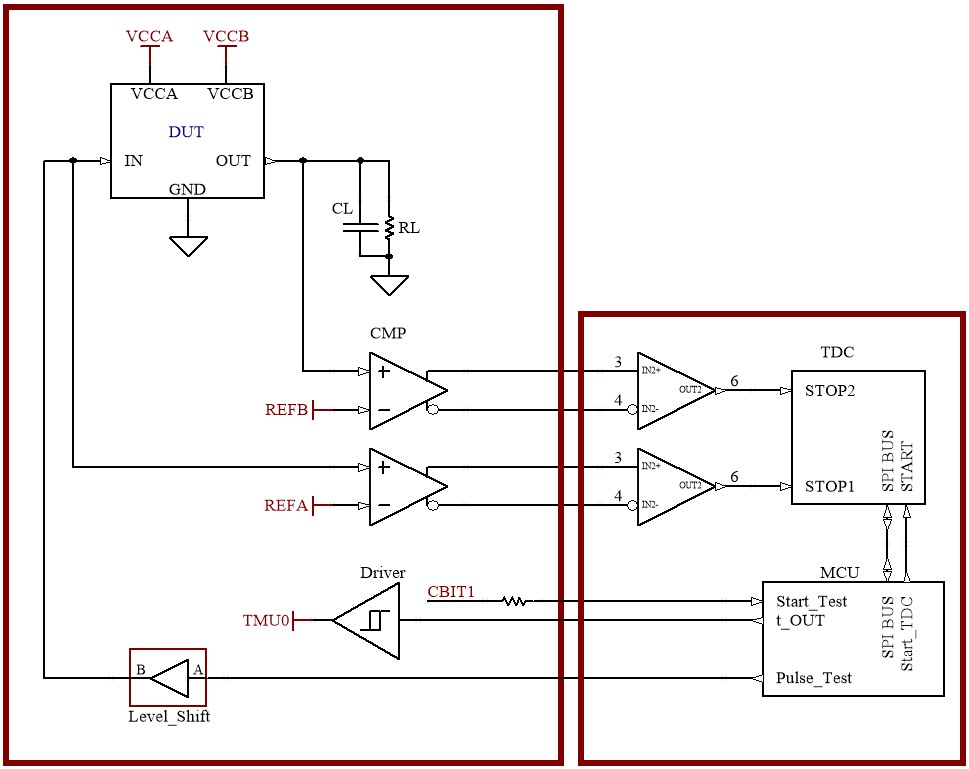

采用TDC的测量方案如图5所示,测试机配合单片机MCU实现传输延迟自动化的测量。因为VCCA和VCCB在1V~3.6V间可变,而TDC芯片和MCU的电压是3.3V,所以DUT与TDC之间加了比较器和电平转换器。对于只需要测量3.3V左右一种电压下的时间参数的情况,DUT和TDC可以直连。

MCU用于控制TDC芯片,计算时间参数的结果,以及和测试机通讯。测试机的CBIT1用于通知MCU是否开始测量;Pulse_Test由MCU在开始测量后发送一个起始脉冲信号,作为DUT的输入信号;Level_Shift的作用是电平转换和提供快边沿的信号;t_OUT用于MCU将计算结果发送给测试机。

图5 TS8111基于TDC的传输延迟测量电路

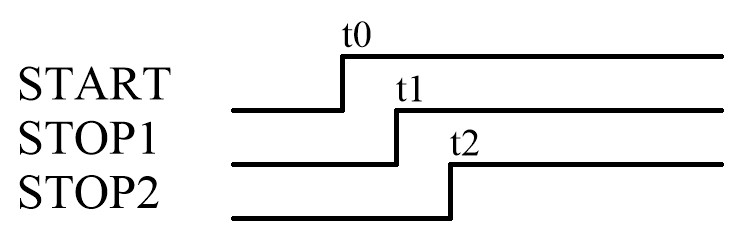

DUT的输入和输出信号各经过一路相同的路径到TDC芯片,作为TDC的两路STOP信号,而TDC的START信号由MCU在发送Pulse_Test之前发送。TDC的测量原理如图6所示。STOP1和STOP2信号的时间间隔t2-t1是通过对“t0到t2的时间长度”和“t0到t1的时间长度”做差求出的,如公式1所示:

t2-t1 = (t2-t0) – (t1-t0) 式1

图6 TDC测量机制

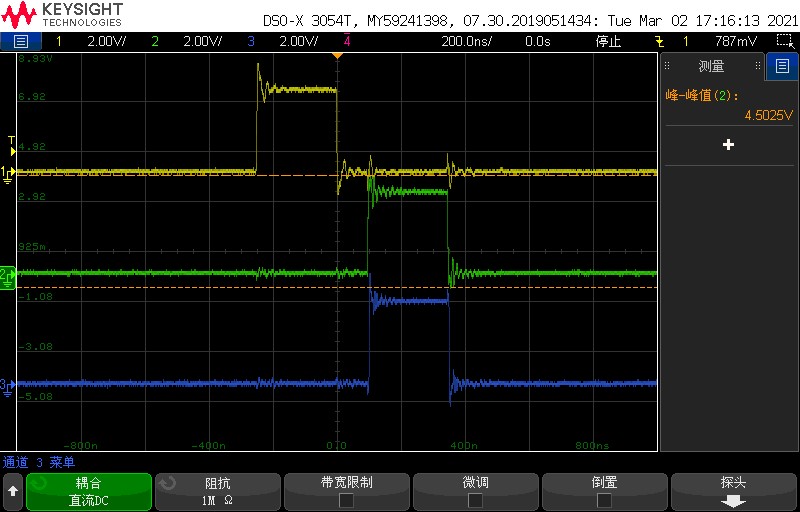

TDC实际测量的波形如图7所示,ch1:START ch2:STOP1 ch3:STOP2,测量tPHL时,捕获START的下降沿和STOP1 STOP2的下降沿;测量tPLH时,捕获START的上升沿和STOP1 STOP2的上升沿;需要满足待测START边沿距离待测STOP边沿的时间大于3.5ns,同时小于2.4us;同时待测边沿的边沿时间要尽量短;

图7 TDC实际测量波形

TDC芯片自动测量的结果正是t2-t1的值,而t2-t1正是DUT的传输延迟,这样就实现了高精度时间间隔的自动化测量。

将TDC测量的值和示波器测量值比对验证,数据基本吻合。TDC测量的结果经过多次求平均可进一步提高数据稳定性,即使如此依旧缩短了测量时间,提高了测试效率。